- Now it is recognized that they also enable a very useful mode of MOSFET operation, and that the sub- threshold region of operation is as important as the traditional cut-off.

- Request PDF All-MOS subthreshold log filters This article proposes the use of nonlinear capacitors for log filtering thanks to the inner voltage dynamic range compression. The generalized.

- However, the subthreshold regime is pretty nice: The reason that you could consider subthreshold 'slow' is that the current is lower and it takes longer to charge a gate capacitor of a fixed size; however, you have fewer higher order effects. For the best power processing per-Watt, you can just design to run in subthreshold at near threshold.

This video is continuation of previous video where gm of MOSFET in strong inversion region was discussed. Video begins with the MOSFET in strong inversion an. Subthreshold leakage — or subthreshold conduction or subthreshold drain current is the current that flows between the source and drain of a MOSFET.

What do you need to know to understand this topic?

- Circuit theory

Sections

What is the subthreshold operation?

In MOSFET model, it was assumed that current only flows through the MOSFET channel when $V_{GS}>V_{TH}$. In reality, current flows even when $V_{GS}$ is below the threshold voltage, but it is orders of magnitude weaker than currents in strong inversion. The inversion layer that is seen in strong inversion is barely seen in this case, and this regime can also be called weak inversion.

Under weak inversion, the relation between current and gate-source voltage becomes exponential, according to the following equation for a NMOS:$$begin{equation}I_{DS} = I_S frac{W}{L}e^{frac{V_{GB}}{nV_T}}left(e^{-frac{V_{SB}}{V_T}} - e^{-frac{V_{DB}}{V_T}} + frac{V_{DS}}{V_A}right)label{eq:subthresholdeq1}end{equation}$$$I_S$ is a characteristic current that defines the current that leaks through the transistor, $W$ and $L$ are the transistor's width and length, $n$ is the subthreshold slope factor (around 1~1.5) and defines the effect that the gate voltage has on the drain current, and $V_T=kT/q$ is the thermal voltage. $V_A$ is the Early voltage, a fictious voltage that represents the influence that $V_{DS}$ has on the drain-source current.For a PMOS, the expression is similar, just replacing the signs in the exponentials:$$I_{DS} = I_S frac{W}{L}e^{-frac{V_{GB}}{nV_T}}left(e^{frac{V_{SB}}{V_T}} - e^{frac{V_{DB}}{V_T}} + frac{V_{SD}}{V_A}right ).$$Continuing with the NMOS and considering the usual case that the source is at the same potential as the bulk ($V_S=V_B$), $eqref{eq:subthresholdeq1}$ simplifies to$$begin{equation}I_{DS} = I_S frac{W}{L}e^{frac{V_{GS}}{nV_T}}left(1 - e^{-frac{V_{DS}}{V_T}} + frac{V_{DS}}{V_A}right)label{eq:subthresholdeq2}end{equation}.$$

Saturation

Similarly to the strong inversion, the weak inversion has a $V_{DS}$ point after which $V_{DS}$ has a weak influence on the drain current. This point was previously called saturation point. In the weak inversion operation, $V_{DS}$ influence becomes small when the term $e^{-frac{V_{DS}}{V_T}}$ is close to 0. That happens when $V_{DS} > 4V_T$: considering that $V_T$~26 mV at room temperature, the saturation point is at ~104 mV. This is a big difference between weak and strong inversion, the saturation point does not depend on the gate voltage or any device parameters and it is rather low. The influence thereafter of $V_{DS}$ in $I_{DS}$ becomes proportional to $V_A^{-1}$.

Small-signal model

The small-signal model in subthreshold is the same as in the strong inversion, although the parameters are calculated differently.As a recap:

It follows several parameters:$$g_m = frac{partial I_{DS}}{partial V_G} = frac{I_{DS}}{nV_T}$$$$g_{mb} = frac{partial I_{DS}}{partial V_B} = frac{(n-1)I_{DS}}{nV_T}$$$$frac{1}{r_o} = g_o = frac{partial I_{DS}}{partial V_{DS}} = frac{I_{DS}}{V_A}$$Extrinsic capacitances such as overlap capacitances $C_{ov}$, depletion junction capacitances $C_{sb}$ and $C_{db}$ and oxide capacitance $C_{ox}$ are independent of the drain current and remain equal to the weak inversion case.Intrinsic capacitances depend on the bias condition, because they represent a fraction of the gate oxide capacitance $WLC_{ox}$.The capacitances from gate to source/drain are only defined by the overlap capacitances, since there is no channel.$$C_{gs} = WC_{ov}$$$$C_{gd} = WC_{ov}$$On the other hand, $C_{gb}$ increases because there is no channel to shield the gate from the substrate (the channel is 'floating' and there is a capacitive path between gate and bulk defined by $C_{ox}$ and $C_{dep}$)$$C_{gb} = frac{n-1}{n}WLC_{ox} = kappa WLC_{ox}$$$$C_{ds} = negligible$$Therefore, $C_{gb}$ becomes the dominant capacitance in subthreshold operation.

Unity-gain frequency

In the weak inversion case, the dominant capacitance is $C_{gb}$ instead of $C_{gs}$. Therefore, the unity-gain frequency is$$f_T = frac{g_m}{2pi C_{gb}}.$$

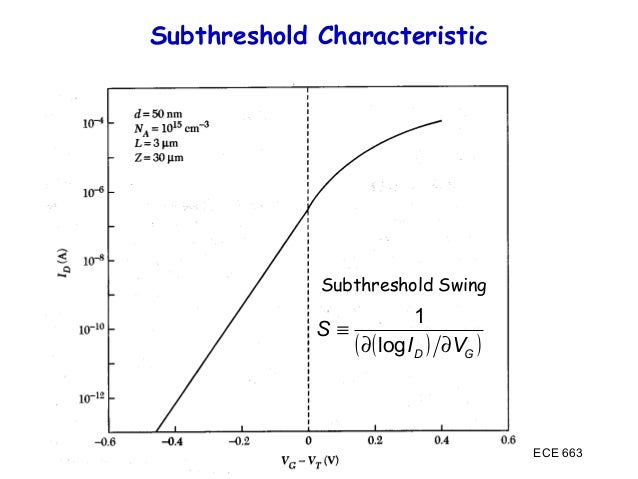

The subthreshold slope

The subthreshold slope $S$ is an important parameter for switches because it defines how much is the ratio between the on and off currents. To get high on/off current ratios, we would like low subthreshold slopes so that the same difference in $V_{GS}$ can decrease the drain current by more decades.

Returning to $eqref{eq:subthresholdeq2}$, let's find out how much $V_{GS}$ needs to decrease in order to reduce the drain current by one decade:$$S = frac{partial V_{GS}}{partial log I_{DS}}$$$$frac{1}{S} = frac{partial log I_S frac{W}{L}e^{frac{V_{GS}}{nV_T}}left(1 - e^{-frac{V_{DS}}{V_T}}right)}{partial V_{GS}}$$$$frac{1}{S} = frac{partial log e^{frac{V_{GS}}{nV_T}}}{partial V_{GS}}$$$$frac{1}{S} = frac{partial frac{ln e^{frac{V_{GS}}{nV_T}}}{ln 10} }{partial V_{GS}}$$$$frac{1}{S} = frac{partial frac{V_{GS}}{nV_T} }{partial V_{GS}ln 10}$$$$frac{1}{S} = frac{1}{nV_Tln 10}$$$$S = nV_Tln 10$$For $V_T$ ~26 mV (room temperature) and the ideal case of $n = 1$, the ideal subthreshold slope for MOSFETs is ~60mV/decade. However, the feasible slopes are around 70~80 mV/decade. Furthermore, as temperature increases, so does $V_T$ and the subthreshold slope.

Mosfet Subthreshold Leakage Current

Junctionless MOSFETs have a number of advantages over the traditional ones in terms of simplicity of design, manufacturing technology and reducing the impact of the short-channel effects on the device characteristics. However, the known experimental nanowire MOSFETs have high subthreshold currents due to the parasitic bipolar transistor appearance in the closed state. A structural model of a planar SOI in accordance with the technology standards of 90 nm and the route of mathematical modeling have been developed. The influence of the impurity concentration in the SOI MOSFET silicon film on the threshold voltage, the saturation currents and subthreshold currents using TCAD environment has been investigated. The investigation results show that if the impurity concentrations in the working body of the device is below 10 cm and there is no interband tunneling effect, and a parasitic bipolar transistor does not arise, the subthreshold currents decrease to 10 A/μm, while maintaining the saturation currents at an acceptable level, which is significantly lower than those of the conventional MOS transistors.

- Key words:junctionless MOSFET, subthreshold current, interband tunneling, impurity concentration

- Published in:integrated electronics elements

- Bibliography link: Korolev M.A., Klyuchnikov A.S., Efimova D.I. Junctionless MOS-transistor with low subthreshold current // Proc. of Universities. Electronics. – 2018. – Vol. 23. – № 2. – P. 186–193. DOI: 10.24151/1561-5405-2018-23-2-186-193

Mosfet Subthreshold Region Equation

National Research University of Electronic Technology, Moscow, Russia

Mosfet Subthreshold Current Equation

National Research University of Electronic Technology, Moscow, Russia

Mosfet Subthreshold Region

2. Colinge J.P. et al. Nanowire transistors without junctions. Nature Nanotechnol., 2010, vol. 5, no. 3, pp. 225–229.

3. Gundapaneni S., Bajaj M., Kottantharayil A., Murali K. Effect of band-to-band tunneling on junctionless transistors. IEEE Trans. Electron Devices, 2012, vol. 60, no. 4, pp. 1021–1030.

4. Ghosh B., Bal P., Mondal P. A junctionless tunnel field effect transistor with low subthreshold slope. Springer Science, 2013, pp. 487–499.

5. Migita S., Morita Y., Matsukawa T., Masahara M. Experimental demonstration of ultrashort-channel junctionless FETs utilizing atomically sharp V-grooves on SOI, IEEE Trans. Nanotechnol., 2014, vol. 13, no. 2, pp. 208–215.

6. Jagadesh Kumar M., Sahay S. Controlling BTBT induced parasitic BJT action in junctionless FETs using a hybrid channel. IEEE Transactions on Electron Devices, 2016, vol. 63, no. 8, pp. 3350–3353.

7. Korolev M.A., Krupkina T.Yu., CHaplygin Yu.A. Priborno-tekhnologicheskoe modelirovanie pri razrabotke izdelij mikroelektroniki i mikrosistemnoj tekhniki [Instrument and technological modeling at development of products of microelectronics and microsystem equipment]. Izvestiya vuzov. Elektronika – Proceedings of Universities. Electronics, 2005, no. 4-5, pp.64–71. (In Rus-sian).